# Oil-Well Monitoring System

# Senior Design I

December 6, 2010

Louis Bengston Jimit Shah Kaleb Stunkard

Sponsored by Harris Corporation

# **Contents**

| Chap | pter | 1:                   | Project Definition                  | . 1 |  |  |  |  |

|------|------|----------------------|-------------------------------------|-----|--|--|--|--|

| 1    | .1   | Execu                | utive Summary                       | 1   |  |  |  |  |

|      |      | 1.1.1                | Hardware Components                 | . 1 |  |  |  |  |

|      |      | 1.1.2                | Software Components                 | . 2 |  |  |  |  |

| 1    | .2   | Motiv                | Motivation                          |     |  |  |  |  |

| 1    | .3   | Goals                | S                                   | 2   |  |  |  |  |

| 1    | .4   | Objec                | ctives                              | 3   |  |  |  |  |

|      |      | 1.4.1                | Hardware                            | . 3 |  |  |  |  |

|      |      | 1.4.2                | Software                            | . 3 |  |  |  |  |

| 1    | .5   | Requi                | irements and Specifications         | 3   |  |  |  |  |

|      |      | 1.5.1                | General Specifications              | . 3 |  |  |  |  |

|      |      | 1.5.2                | Hardware                            | . 4 |  |  |  |  |

|      |      | 1.5.3                | Software                            | . 7 |  |  |  |  |

|      |      | 1.5.4                | System Protection                   | . 7 |  |  |  |  |

| 1    | .6   | Budget and Financing |                                     |     |  |  |  |  |

| Chap | pter | 2:                   | Research                            | . 9 |  |  |  |  |

| 2    | 2.1  | Previo               | Previous Works and Similar Works9   |     |  |  |  |  |

| 2    | 2.2  | Hardy                | Hardware Research9                  |     |  |  |  |  |

|      |      | 2.2.1                | AC-DC Rectification                 | . 9 |  |  |  |  |

|      |      | 2.2.2                | DC-DC Step Down Conversion          | 13  |  |  |  |  |

|      |      | 2.2.3                | Analog to Digital Signal Conversion | 16  |  |  |  |  |

|      |      | 2.2.4                | MOSFET Driver                       | 19  |  |  |  |  |

|      |      | 2.2.5                | Controllers                         | 20  |  |  |  |  |

|      |      | 2.2.6                | Op-Amps                             | 41  |  |  |  |  |

|      |      | 2.2.7                | Power Factor Correction             | 42  |  |  |  |  |

|      |      | 2.2.8                | Global Positioning System           | 42  |  |  |  |  |

| 2    | 2.3  | Softw                | are Research                        | 47  |  |  |  |  |

|      |      | 2.3.1                | User Interface                      | 47  |  |  |  |  |

|      |      | 2.3.2                | PC Communication                    | 47  |  |  |  |  |

|      |      | 2.3.3                | Power Factor Correction (PFC)       | 47  |  |  |  |  |

|      |      | 2.3.4                | GPS                                 | 48  |  |  |  |  |

|      |      | 2.3.5                | Digital Controller                  | 48  |  |  |  |  |

|      |      |                      |                                     |     |  |  |  |  |

|         | 2.3.6              | PIC Microcontroller                  | 49  |  |

|---------|--------------------|--------------------------------------|-----|--|

| Chapter | 3:                 | Design                               | 51  |  |

| 3.1     | 1 Hardware         |                                      |     |  |

|         | 3.1.1              | AC/DC Rectifier with Boost Converter | 51  |  |

|         | 3.1.2              | DC-DC Converter                      | 60  |  |

|         | 3.1.3              | Charging Circuit Design              | 69  |  |

|         | 3.1.4              | Global Positioning System            | 75  |  |

|         | 3.1.5              | System Packaging                     | 82  |  |

| Chapter | 4:                 | Testing                              | 84  |  |

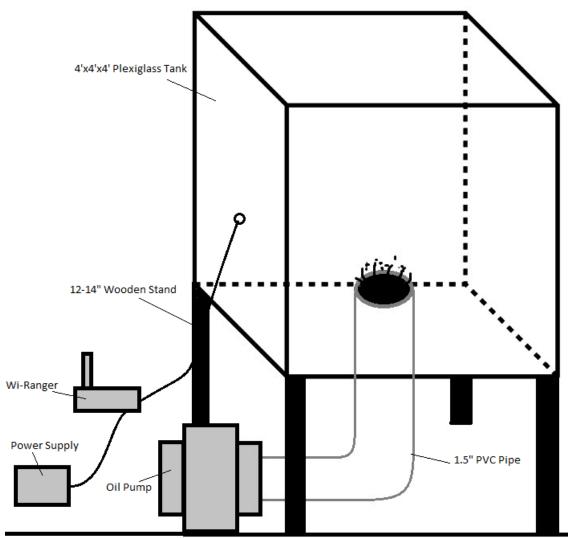

| 4.1     | Test I             | Facility                             | .84 |  |

| 4.2     | Testing Procedures |                                      |     |  |

| 4.3     | Comr               | nunication                           | .86 |  |

| 4.4     | Syste              | m Test                               | .87 |  |

| Chapter | 5:                 | Summary                              | 89  |  |

|         | 5.1.1              | Parts Procurement                    | 89  |  |

|         | 5.1.2              | Conclusion                           | 90  |  |

# List of Tables

| 1.1 - Eletrical Specifications of Ginlong Generator                    | 4    |

|------------------------------------------------------------------------|------|

| 2.1 - Comparison of Control Methods for the VIENNA Rectifier           |      |

| 2.2 - Comparison of Synchronous versus Asynchronous Converters         | . 15 |

| 2.3 - Comparison of Power Losses for Synchronous and Asynchronous Buck |      |

| Converters                                                             | . 16 |

| 2.4 - Resolution amount for 8-Bit system to 24-Bit system              | . 17 |

| 2.5 - Parameters for the LM5101A Driver                                | . 19 |

| 2.6 - Parameters for the ADP3625 Driver                                | . 20 |

| 2.7 - Parameters for the LTC4440-5 Driver                              | . 20 |

| 2.8 - Parameters for the PIC10F222 Microcontroller                     | . 22 |

| 2.9 - Parameters for the PIC12F683 Microcontroller                     | . 22 |

| 2.10 - Parameters for the PIC16F886 Microcontroller                    | . 23 |

| 2.11 - Parameters for the PIC18F2620 Microcontroller                   | . 24 |

| 2.12 - Parameters for the dsPIC33FJ16GS504 Microcontroller             | . 24 |

| 2.13 - Oscillator Clock Modes for the dsPIC33FJ16GS504                 | . 40 |

| 3.1 - Controller coefficients for Digital Signal Processor             | . 55 |

| 3.2 - Parameters of the LM5116WG Buck Converter                        |      |

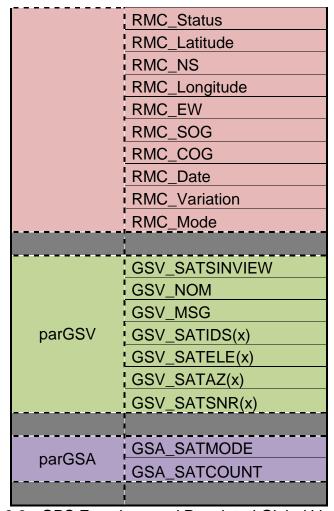

| 3.3 - GPS Functions and Populated Global Variables                     | . 80 |

# List of Figures

| 1.1 - Gantt Chart for Projected Project Completion, Electrical Team         | 3  |

|-----------------------------------------------------------------------------|----|

| 1.2 - Power v. Rotation Speed and Voltage v. Rotation Speed for the Ginlong |    |

| generator                                                                   |    |

| 1.3 - Development Kit                                                       |    |

| 2.1 - Three-Phase Full Wave Rectifier Circuit                               | 10 |

| 2.2 - VIENNA Rectifying Circuit                                             | 11 |

| 2.3 - Hysteresis Control Method for the VIENNA Rectifier                    | 12 |

| 2.4 - Constant Frequency Control Method for the VIENNA Rectifier            |    |

| 2.5 - Asynchronous Buck Converter                                           | 15 |

| 2.6 - Synchronous Buck Converter                                            |    |

| 2.7 - 8-bit Analog to Digital Converter Circuit                             | 18 |

| 2.8 - Pin Layout for the dsPIC33FJ16GS504                                   |    |

| 2.9 - Pin Description for the dsPIC33FJ16GS504                              | 26 |

| 2.10 - Pin Description for the dsPIC33FJ16GS504                             | 27 |

| 2.11 - Minimum Recommended Connections for Decoupling Capacitors for the    |    |

| dsPIC33FJ16GS504                                                            |    |

| 2.12 - Recommended Connection for the Master Clear Pin for the              |    |

| dsPIC33FJ16GS504                                                            | 29 |

| 2.13 - Recommended Placement of the Oscillator Circuit for the              |    |

| dsPIC33FJ16GS504                                                            | 30 |

| 2.14 - Synchronous Buck Converter Circuit with dsPIC33FJ06GS202             | 31 |

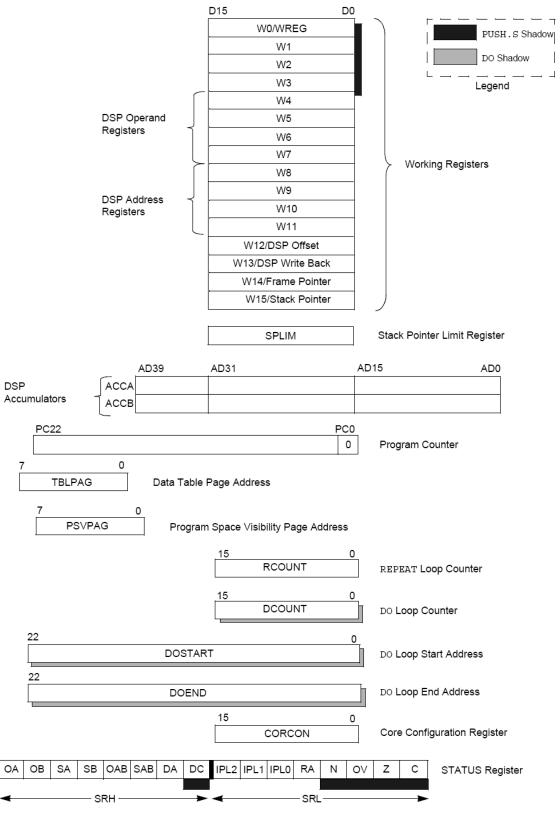

| 2.15 - CPU Block Diagram for the dsPIC33FJ16GS504                           | 32 |

| 2.16 - CPU Programmer's Model for the dsPIC33FJ16GS504                      | 33 |

| 2.17 - CPU Status Register Designation for the dsPIC33FJ16GS504             |    |

| 2.18 - Core Control Register Designation for the dsPIC33FJ16GS504           |    |

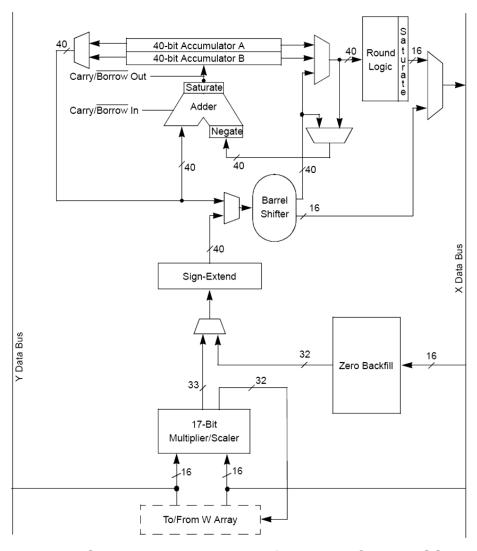

| 2.19 - DSP Engine Block Diagram for the dsPIC33FJ16GS504                    | 36 |

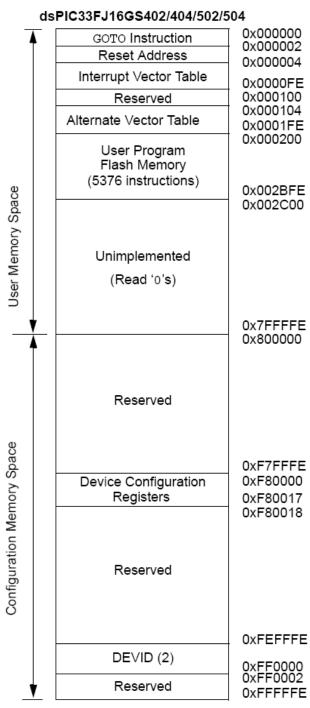

| 2.20 - Program Memory Map for the dsPIC33FJ16GS504                          | 37 |

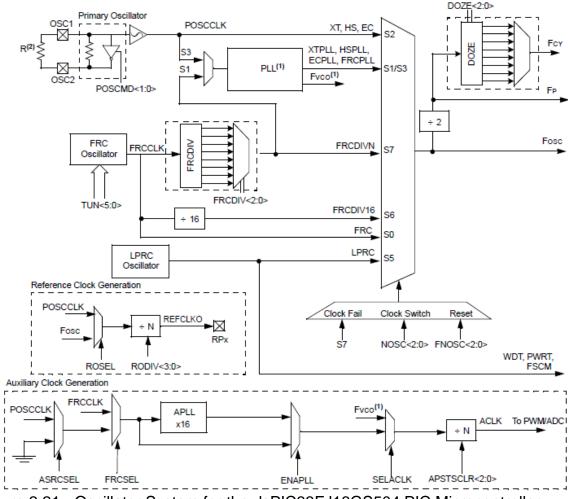

| 2.21 - Oscillator System for the dsPIC33FJ16GS504                           | 39 |

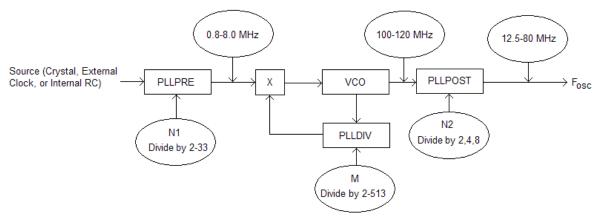

| 2.22 - PLL Block Diagram for the dsPIC33FJ16GS504                           | 40 |

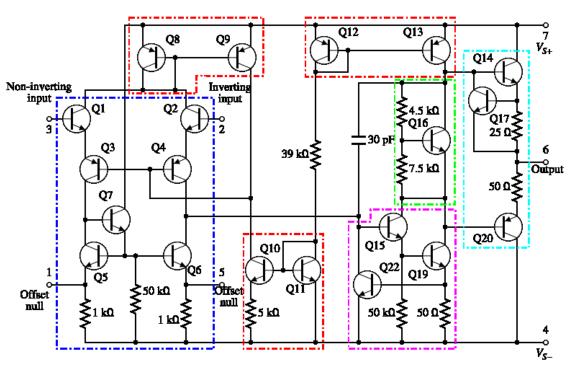

| 2.23 - Operational Amplifier Internal Circuitry                             | 41 |

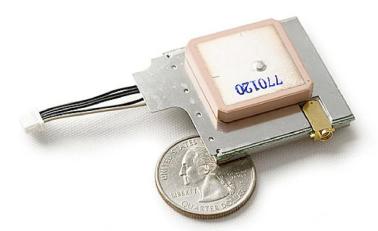

| 2.24 - EM-406A GPS Receiver                                                 |    |

| 2.25 - EM-408 GPS Receiver                                                  | 45 |

| 2.26 - NAVIBE 611 Sport GPS Module                                          | 46 |

| 2.27 - Holux GPSlim236 Module                                               | 46 |

| 2.28 - Block Diagram of a PID Controller                                    | 49 |

| 3.1 - Complete Block Diagram of Power Management Circuit                    | 51 |

| 3.2 - Plant Control Model of VIENNA Rectifier                               | 52 |

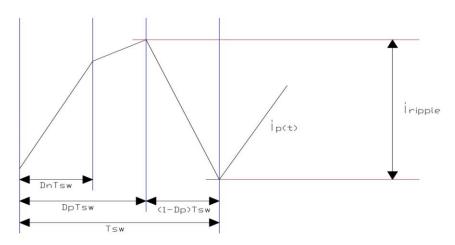

| 3.3 - Positive Side Current Waveform when Dp > Dn                           | 52 |

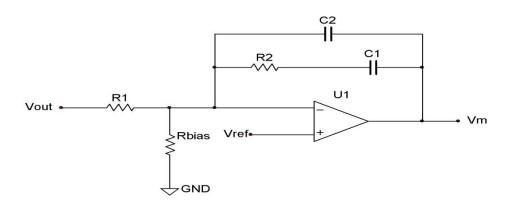

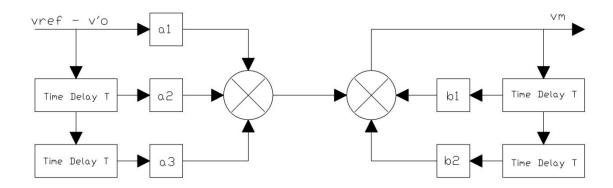

| 3.4 - Analog Type II Compensator Implemented with Operational Amplifier     |    |

| 3.5 - Digital Lag-Lead Compensator Flow Diagram                             |    |

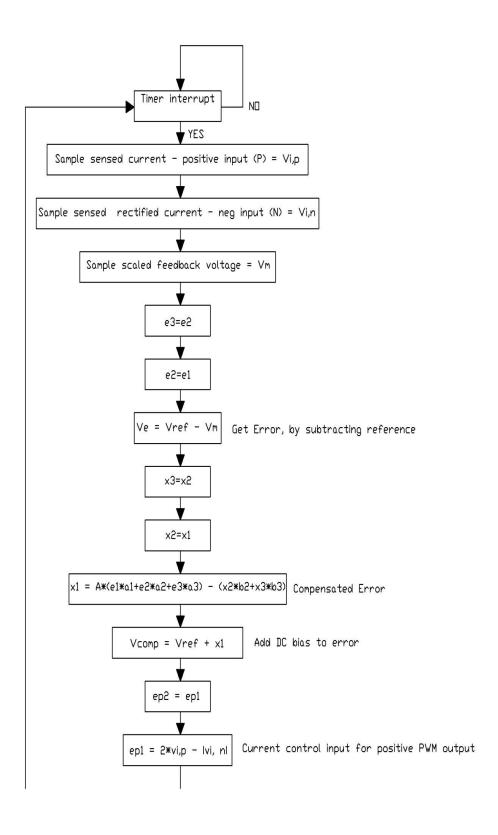

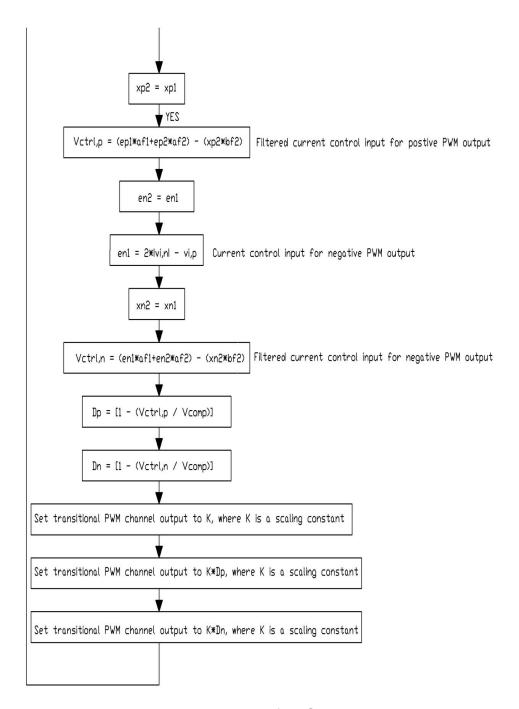

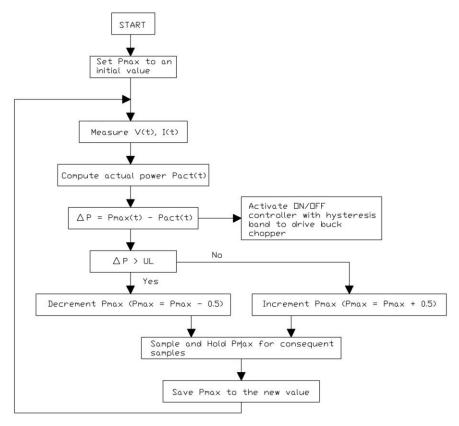

| 3.6 - Flow Diagram of PFC digital controller                                | 58 |

| 3.7 - Flowchart of Proposed MPPT Algorithm                                  | 59 |

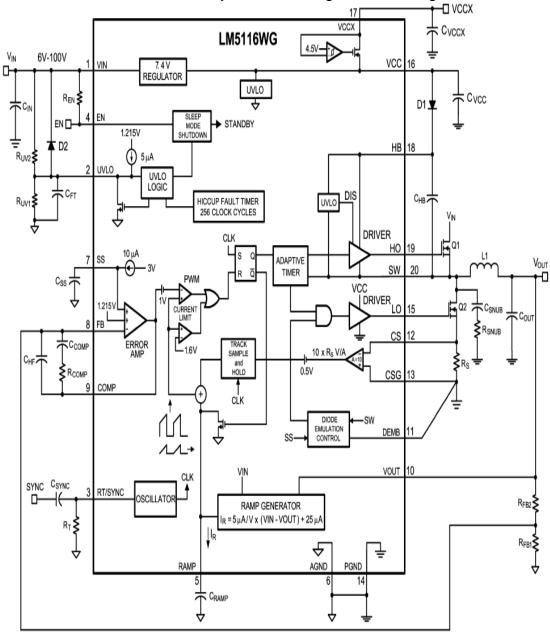

| 3.8 - Block Diagram of the LM5116WG Converter                               | 61 |

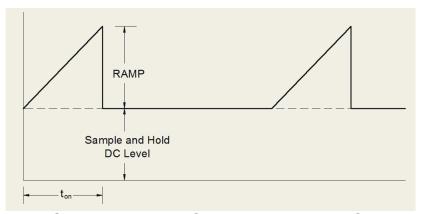

| 3.9 - Sample and Hold DC Level and Emulated Current Ramp                    |    |

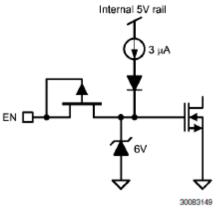

| 3.10 - Enable Circuit                                                   | 63 |

|-------------------------------------------------------------------------|----|

| 3.11 - Current Limit and Ramp Circuit                                   | 64 |

| 3.12 - LM5116WG Modular Gain and Phase                                  | 66 |

| 3.13 - Error Amplifier Gain and Phase                                   | 67 |

| 3.14 - Overall Voltage Loop Gain and Phase                              |    |

| 3.15 - Complete Buck Converter circuit with calculated component values | 69 |

| 3.16 - Manual microprocessor solution to power 4-pack battery           | 70 |

| 3.17 - Off-the-shelf IC solution to power 4-pack battery                | 71 |

| 3.18 - Microcontroller charger circuit schematic                        | 73 |

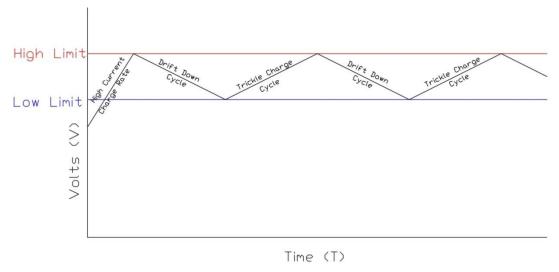

| 3.19 - Battery Charging Strategy Utilized in Charging Circuit           | 75 |

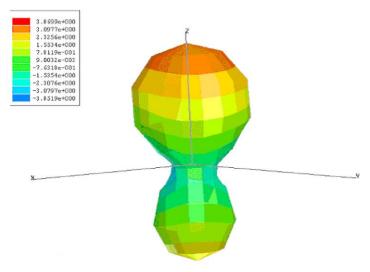

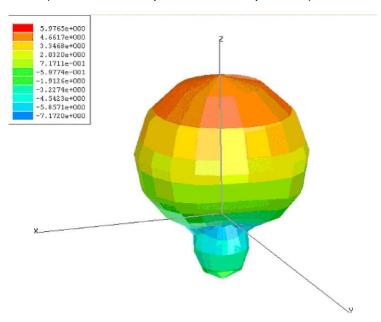

| 3.20 - 3-D representations of Antenna Ground Plane Characteristics      | 76 |

| 3.21 - 3-D representations of Antenna Ground Plane Characteristics      | 76 |

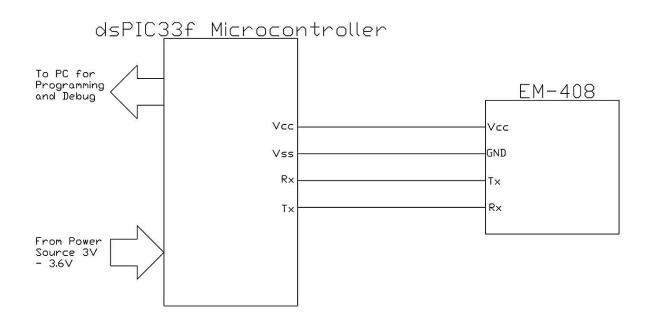

| 3.22 - Interfacing EM-408 GPS Module to dsPIC33f Microcontroller        | 77 |

| 3.23 - External Magnet Mount GPS Antenna                                | 81 |

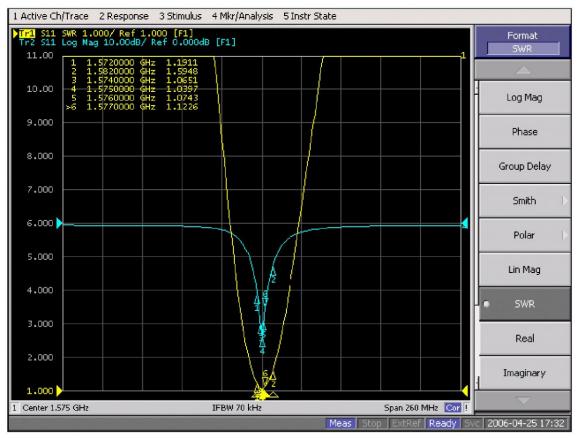

| 3.24 - Standing Wave Ratio of External Antenna                          | 81 |

| 3.25 - MMCX to SMA Interface Cable                                      | 82 |

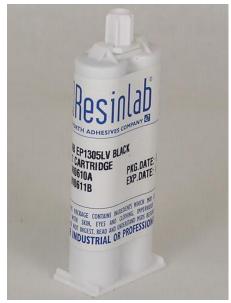

| 3.26 - Two-Part Formula EP 1305 LV Black Epoxy Potting Compound         | 82 |

| 3.27 - Non-Metallic NEMA 4X Weatherproof Enclosure                      | 83 |

| 4.1 - System Test Rig                                                   | 88 |

| 5.1 - Parts List                                                        |    |

## Chapter 1: Project Definition

# 1.1 Executive Summary

Hydrocarbons and their derivatives are a vital energy source for the world. This energy source must be managed effectively. Failure to do so often results in severe economic and environmental damage. Oil spills/leaks still remain an area of hydrocarbon management that needs improvement. The Gulf of Mexico alone is home to 27,000 abandoned oil well heads. Currently, there is no monitoring system in place to detect oil leakage from these abandoned wells. A system with the ability to actively prevent, monitor and respond to oil spills is desperately needed.

A small army of engineers has been assembled to develop such a system. A plethora of oil detection senor packages can be developed to detect underwater oil leaks. However, all of these packages require power. Obtaining useful electrical energy in the middle of the ocean is not an easy task. Nature provides three main sources of convertible energy. These include: solar, wind, and waves. A mechanical energy team has decided to design and build a hydro turbine to power a generator. Deep water ocean waves will move water over the turbine causing it to rotate. The wave generator will be placed on a large buoy that is tethered to the underwater apparatus. Several factors influence the magnitude, direction and frequency of waves. Thus, ocean waves fluctuate at random. The latter directly impacts the output of the generator. The output of the generator will be a signal of variable voltage, current and frequency. Such a signal can't be used by any electronic components. Additionally, the generator is only efficient if it operates above a particular RPM. Thus, the electrical energy from this generator must be efficiently managed, converted and stored for use by the remaining components of the system.

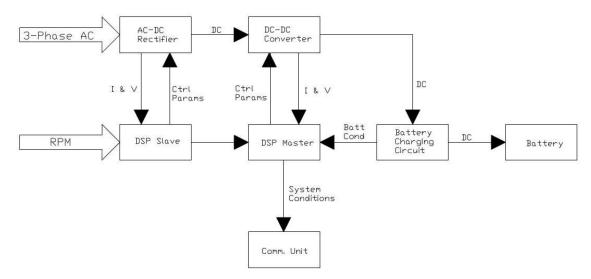

The team will analyze, design, build and test a low cost power management circuit. The AC signal will first be converted to high voltage DC. A step down DC-to-DC converter will bring the DC voltage down to a useable level. Also, the circuit will utilize effective control mechanisms to automatically adjust the load based on RPM input. Excess power will be stored in a battery. Power efficiency will be achieved with Maximum Power Point Tracking (MPPT). A charging circuit will be integrated into the design to allow the charging of many different types of batteries. Lastly, it will be designed to withstand harsh condition and outfitted with GPS to verify the buoy's tether remains intact.

#### 1.1.1 Hardware Components

All of the main hardware components will be placed on one printed circuit board. The components include:

- Converters (AC-DC, DC-DC)

- Controllers

- Power Supply

- Charging Circuit

- GPS

The PCB board will be housed inside a weatherproof enclosure.

#### 1.1.2 Software Components

The software components can be split into two main sections. PC Software will be used to interact with and reprogram the digital controllers. The controller itself will also run software that will perform some basic arithmetic.

#### 1.2 Motivation

Energy management solutions have gained significant ground in recent years. With the push for going green, obtaining maximum energy efficiency is in high demand. The electrical engineering group would like to contribute valuable research into advanced power electronics. Hopefully the design has a significant positive impact on the clean-energy movement. The group also looks forward to representing the United States, the University of Central Florida, and Harris Engineering Corporation.

#### 1.3 Goals

Harris Engineering Corporation will be using this system as part of their oil detection monitoring system. Therefore, success will be determined by meeting the following goals outlined below:

- 1. Maximize the energy supplied from the wave generator.

- 2. Charge several different types of batteries.

- 3. Protect against battery overcharging.

- 4. Operate over a range of 60 to 240 rpm.

- 5. Operate when the generator output voltage is less than the battery voltage.

- Outfitted with GPS

- 7. Allow operator to monitor and control the system.

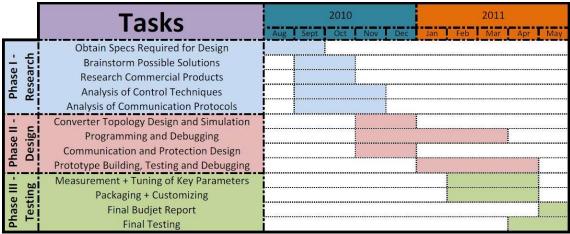

Completing these 7 steps in a timely manner is critical. The Gantt chart in Figure 1.1 will be closely followed.

Figure 1.1 - Gantt Chart for Projected Project Completion, Electrical Team

# 1.4 Objectives

#### 1.4.1 Hardware

The hardware objectives start with specifying the inputs and outputs of the system. The wave generator's output will be used as the input to the system. The system's output will be connected to a battery and sensor package. The system's goal is to transfer the power from the input to the output in the most efficient manner possible. Efficiency will be verified by connecting the system to a computer. All of the electronic components will be fitted onto a single PCB. The objectives above will be accomplished while maintaining a low parts cost.

#### 1.4.2 Software

The software objectives are limited to PC software and controller software. The PC software will be used to program and monitor the system. Having a PC interface simplifies the development process while providing excellent logging capabilities. The onboard controller software will run a simple algorithm to help pinpoint what changes need to be made during the conversion to maintain maximum efficiency.

# 1.5 Requirements and Specifications

#### 1.5.1 General Specifications

Harris Corporation has assigned four groups: three mechanical engineering groups and one electrical engineering group to be a part of this project. The mechanical engineering groups together will be in charge of development of

turbine, buoy and the sensor package. The electrical engineering group has been assigned to make sure that the necessary power is supplied to the system.

The hardware must meet the requirements as stated by Harris Corporation. According to these requirements, the system must meet the following:

- Efficiently convert a varying AC signal to a conditioned DC voltage.

- Develop an energy storage method which can continuously deliver power to the sensors.

- Design an automated generator load control system which can optimize the load control for varying input forces and generator RPM's.

- Create a GPS system which can determine and relay the buoy position for a given time.

- Create a wireless transmitter to broadcast the results of the underwater sensors.

- Must be able to work in high and low pressure environment.

- Suitable for dry and under water environment.

#### 1.5.2 Hardware

**Ginlong Generator Specifications** — A Ginlong generator (Model #GL-PMG-500A) is ready to be used to develop wave energy. The electrical specifications of this generator are shown in Table 1.1

| Electrical Specifications                     |                                  |  |  |  |

|-----------------------------------------------|----------------------------------|--|--|--|

| Rated Output Power(W)                         | 500                              |  |  |  |

| Rated Rotation Speed (RPM)                    | 450                              |  |  |  |

| Rectified DC Current at Rated Output (A)      | 20                               |  |  |  |

| Required Torque at Rated Power                | 14.8                             |  |  |  |

| Phase Resistance (Ohm)                        | 5                                |  |  |  |

| Output Wire Square Section (mm <sup>2</sup> ) | 4                                |  |  |  |

| Output Wire Length (mm)                       | 600                              |  |  |  |

| Insulation                                    | H Class                          |  |  |  |

| Generator configuration                       | 3 Phase star connected AC output |  |  |  |

| Design Lifetime                               | >20 years                        |  |  |  |

Table 1.1 - Eletrical Specifications of Ginlong Generator (Permissions requested from Ginlong Technologies, Inc.)

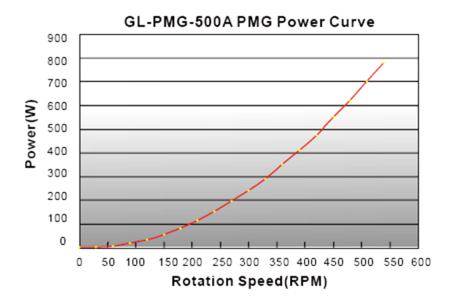

Because the generator will be turned by wave energy harnessed through a uniquely designed turbine system, it is expected that the rotations per minute of the generator will vary significantly. No load will be placed upon the generator at startup, but the load control circuitry will ultimately be responsible for maintaining the steadiest possible rotation in the generator. Figure 1.2 shows the power (W) and voltage (V) outputs for the Ginlong generator as functions of rotation speed

(RPM). The power output is very low and grows very slowly for low rotation speeds, but at higher rotation speeds, the power output begins to climb more rapidly. The voltage output has an approximately linear relationship with rotation speed, where the voltage in volts is equal to one tenth of the rotation speed in RPM.

Figure 1.2 - Power v. Rotation Speed and Voltage v. Rotation Speed for the Ginlong generator (Permission requested from Ginlong Technologies, Inc.)

**Sensor Power Requirements** — Sensor power requirements need to be met in an efficient manner. The sensor package will be the most critical part of the project since this package will be responsible for detecting the presence of oil in

water. The sensor team will be using a Wi-Ranger to power the components (sensors, DAQ, etc.). In order to provide an efficient power supply, the Wi-Ranger specs need to be taken under consideration. According to the datasheet, the Wi-Ranger requires an external power supply with 5V DC and 3A which is 15W.

**Control System** — The Control System will be comprised of:

- AC-DC Rectifier

- DC-DC Buck Convertor

- PWM controller

- Analog to Digital Convertor

An **AC-DC Rectifier** will be needed to rectify the input AC signal to output DC signal. Here are the various requirements for the rectifier:

- Three phase input

- Must be able to control a sinusoidal input current

- Maintain input current to be in phase with input voltage

- Variable frequency, voltage and current

- Produce a constant DC-bus

- Generate PWM signals

A **DC-DC Converter** must regulate the input DC signal coming from the rectifier to a constant DC output signal. A major problem in creating such a converter would be its fluctuating output due to the varying nature of the wave speed. Hence, the converter will need to meet or exceed the following expectations:

- Large input voltage capability, up to 100V

- Must be able to produce a constant output voltage of 5V DC and constant output current of 3A

- Maintain low voltage ripple

- Implement error compensation loop

- Must maintain high efficiency levels

**GPS Requirements** — A GPS system needs to be developed in order to track the buoy. There are a few options to go about developing this system. However, the most efficient option was the one with following requirements:

- Sends one heartbeat signal per day.

- Sends an alarm when the buoy is positioned out of its desired radius.

- Returns to sleep mode when not in use.

- Is compact and easy to install

- Operates on low power.

**Circuit Charging Design** – An efficient circuit charging design needs to be implemented that can meet or exceed the following requirements:

- Maximize long term charging capacity

- Provide accuracy

- Be able to communicate in various conditions

- Maintain high level efficiency

- Be cost-efficient

#### 1.5.3 Software

**Generator** — A software system is being used in order to simulate and test the generator results.

**Load Control** — Simulation tools needs to be developed that will test the system on the following concepts:

- Stability

- Voltage Regulation

- Frequency Regulation

- Power Quality

- Load Leveling

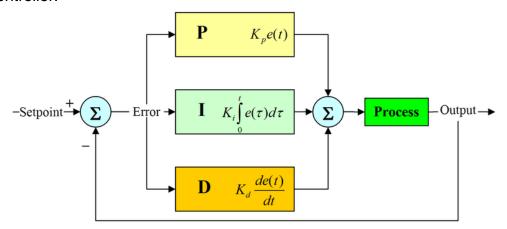

**Digital Controller** – A digital controller must be placed in order to compensate for error in the power systems. Here are the requirements:

- Compensate for steady-state and overshooting errors

- Maintain flexibility for rapidly changing outputs

- Easily tuned in order to achieve desirable results

- Must be able to collect data, produce various models and provide efficient tuning capabilities

**GPS System** — In order to track the buoy in an efficient manner, tracking software is needed that can fulfill or following requirements:

- User-friendly interface

- Able to produce heart-beat message

- Low power usage

## 1.5.4 System Protection

Since this system will be placed in volatile conditions, necessary steps need to be taken to ensure maximum safety. Hence, utmost care will be taken while choosing components for the design as they need to withstand various parameters such as high voltage, power, pressure, etc. If a situation may arise such that certain components could past the threshold of the parameters mentioned above, it is highly likely to cause permanent damage to the system.

In order to protect the system from such drastic conditions, precautions will be taken. Protection will be implemented in two levels – hardware and software. Also, external protection such as epoxy resin could be used for potting transformers and inductors in order to prevent a short circuit and to maintain a stable, long-lasting life.

# 1.6 Budget and Financing

Due to the nature of the project, the primary costs will be for the components and testing materials. A research lab and certain other facilities will already be available for use. These facilities include PCB maker machine, test rig, hydraulic wave generator simulator, etc. Additionally, a lot of component manufacturers tend to provide discounted or free samples. Figure 1.3 provides an example of a development kit that the team plans on purchasing since the total package of the kit costs less than the individual components.

Figure 1.3 - Development Kit (Permission requested from Mikroelektronics)

The total cost for the electrical team is expected to be less than \$2,000, which will be covered by Harris Corporation.

## Chapter 2: Research

#### 2.1 Previous Works and Similar Works

One of the major hurdles in the research for this project stemmed from the fact that the various aspects of the project were split between several groups. It is necessary to research a variety of power related topics – ranging from AC-DC rectification to DC-DC step down conversion to load control – without having immediate access to information from the other groups. Not knowing definitively the specifications of the power produced by the wave generator, or the power requirements of the sensor package, research had to be conducted on a broader range.

In order to facilitate the research, it was determined practical to investigate similar previous works. While the concept of wave-generated power has existed since the 1870's [1], investigations into wave power were drastically reduced in the 1980's in favor of wind power [2]. As a result, there is a significantly greater quantity of more thorough, readily available information regarding wind power than there is for wave power. In light of the design of the wave power generator and anticipated variation in its power generation resulting from the randomness of waves, it is decided reasonable to make a comparison between the wave power provided by this project and the power provided by modern wind power generators. To this end, various aspects of power management in wind power generators were researched, including but not limited to AC-DC conversion, DC-DC step-down conversion, MOSFETs, and op-amps.

#### 2.2 Hardware Research

#### 2.2.1 AC-DC Rectification

The output from the wave generator is known to be AC electric power of variable magnitude. In order to power the sensor package, this needed to be converted to stable DC electric power. To accomplish this, the first aspect that is researched is AC-DC rectification.

**Full Wave Bridge Rectification** — A simple rectifying circuit is the full wave bridge rectifier, so named for its diode bridge. When the input voltage is positive, two of the diodes are forward biased, while the opposite two are reverse biased, providing a positive output voltage across the resistor. When the input voltage is negative, the diode biases are switched, and a positive output voltage is still produced across the resistor.

While the voltage output for the full wave bridge rectifier is a positive DC voltage, it strongly mirrors the amplitude of the input AC voltage, which is undesirable. It

is also possible to utilize a transformer to reduce the input voltage before it reaches the diode bridge, but an anticipated low maximum power supplied by the wave generator make the necessity for this reduction unlikely.

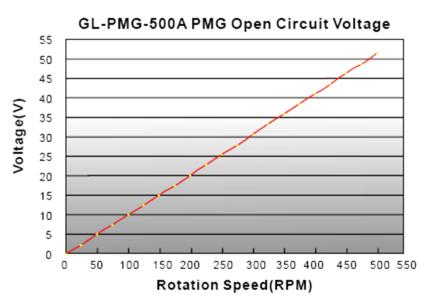

**Three-Phase Full Wave Rectification** — A three-phase full wave rectifying circuit, shown in Figure 2.1, is able to provide a more DC output that is closer to a constant value for a three-phase AC input. This is a result of the fact that the phase difference between the three AC waveforms, when fully rectified, is smaller than the wavelength of any one waveform.

The advantage of this circuit is a significant decrease in the DC voltage's dependency on the amplitude of the AC waveform. This would result in a reduced necessity of ripple attenuation for the DC output. However, the three-phase full wave rectifier requires more components than a full wave bridge rectifier. This would make it more expensive and require more space. It also requires a three-phase AC input.

Figure 2.1 - Three-Phase Full Wave Rectifier Circuit

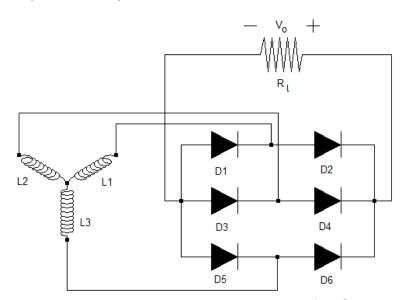

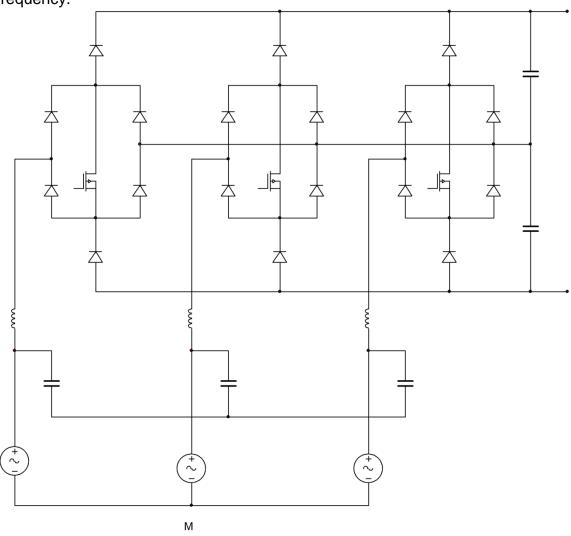

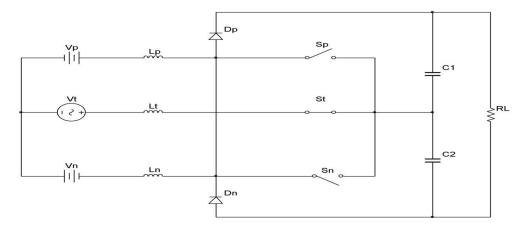

**VIENNA Rectifier** — The VIENNA rectifier is a three-phase, three-level, pulse-width modulation full wave rectifying circuit invented by Johann Kolar <sup>[3]</sup>. The circuit is shown in Figure 2.2.

The VIENNA rectifier is an extension of the full wave bridge rectifier with a boost converter for a higher DC output. It has a unity power factor <sup>[5]</sup>. Other potential advantages to the VIENNA rectifier are high power density and low switching losses. The pulse width modulation would also serve to compensate for the variable frequency power produced by the wave generator.

The VIENNA rectifier has been shown to demonstrate a wide variety of features that make it an excellent choice for this project. One of the requirements for any

rectifying circuit utilized is compatibility with the three-phase Ginlong generator. A power factor as close to one as possible is also desired. The rectifier also needs to be able to handle effectively variable amplitude, variable frequency AC voltage input because of the sporadic nature of the waves turning the generator. The VIENNA rectifier is a natural choice in light of its three-phase input, its high power factor, and its ability to rectify a voltage input with variable amplitude and frequency.

Figure 2.2 - VIENNA Rectifying Circuit

The most significant disadvantage of the VIENNA rectifier is that it functions as a two-switch boost rectifier, resulting in a significantly increased output voltage, the value of which depends on the boost ratio. The boost ratio can vary, but it is expected to be approximately 6.4 the input voltage. For a 25V input from the Ginlong generator, this would result in a voltage output from the VIENNA rectifier of 160V. DC-DC step down conversion would be required to compensate for this effect.

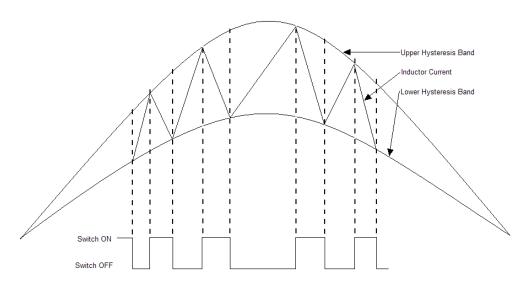

There are two methods of controlling the VIENNA rectifier: the hysteresis control method and the constant frequency method. A graphical depiction of the hysteresis method of control is presented in Figure 2.3. For this method, upper and lower boundaries for inductor current are set. The current is controlled through a switch to maintain a value between the established boundaries. This method has the disadvantage of complexity, but the advantage of its power harmonics being spread over a large range of frequencies.

Figure 2.3 - Hysteresis Control Method for the VIENNA Rectifier

A graphical depiction of the constant frequency control method is presented in Figure 2.4. For this method of control, the control switch is switched at a constant frequency with varying pulse width.

Figure 2.4 - Constant Frequency Control Method for the VIENNA Rectifier

Each of these methods has specific advantages and disadvantages that ought to be considered when deciding how best to control the VIENNA rectifier. Table 2.1 considered the comparative advantages and disadvantages to these two methods.

|               | Control Method                                           |                                    |  |  |

|---------------|----------------------------------------------------------|------------------------------------|--|--|

|               | Constant Frequency Control                               | Hysteresis Control                 |  |  |

|               | Easier EMI filtering                                     | EMI distributed over wide spectrum |  |  |

|               | Simple control implementation                            | Inherent current protection        |  |  |

| Advantages    | Single control loop for output voltage and input current |                                    |  |  |

|               | Automatically balances output capacitor bank             |                                    |  |  |

|               | Requires input voltage state sensing                     | More strict EMI filtering          |  |  |

| Disadventages |                                                          | Requires input voltage sensing     |  |  |

| Disadvantages |                                                          | Requires extra control loop to     |  |  |

|               |                                                          | balance output capacitor bank      |  |  |

|               |                                                          | More complex control algorithm     |  |  |

Table 2.1 - Comparison of Control Methods for the VIENNA Rectifier

In general, the VIENNA rectifier boasts a significant number of advantages over alternative rectifying circuits. These advantages include:

- Low input current harmonic distortion

- Three-level output for compatibility with any DC-DC converter

- Low switch count

- Low control effort in terms of quantity of required gate drives

- Compatibility with variable frequency inputs

### 2.2.2 DC-DC Step Down Conversion

Once the AC power from the wave generator is converted into DC power, it is concluded that it might be necessary to utilize DC-DC step-down conversion to reduce the DC power. In order to accomplish this, various methods of step-down conversion were investigated. These methods, along with applicable benefits and drawbacks, are discussed in this section.

**Voltage Divider** — A voltage divider is a simple, inexpensive tool that could be used to reduce DC power. For a voltage divider, the output voltage across the

load resistor is given by  $V_o = V_i \times \frac{R_l}{R_l + R}$ . This voltage divider is not ideal, as it is highly inefficient, resulting in a constant loss of power equal to  $100 \times \left(1 - \frac{R_l}{R_l + R}\right)$ %. Also, the circuit itself does not contain any inherent control, so a separate circuit would need to be designed in order to provide control options.

**Zener Regulator** — A zener regulator has an additional degree of control provided by the zener diode. The zener diode allows current to pass in the reverse direction under certain conditions that would damage regular diodes, and it can be used to control the output voltage. For this circuit, the output voltage is given by  $V_0 = \frac{R_L(V_i - V_Z - RI_Z)}{R}$ . This is not ideal for voltage regulation, because the zener voltage is dependent on the input voltage and on the load.

**Series Voltage Regulator** — Adding a common collector BJT to the zener regulator results in a series voltage regulator. The presence of the transistor reduces the load on the diode, reducing the fluctuation of zener voltage. This circuit has the capability to regulate a voltage drop with greater stability than the previously discussed regulators, but it is still dependant on the load. All of these regulators also run the risk of overheating if the difference between the input and output voltage is large.

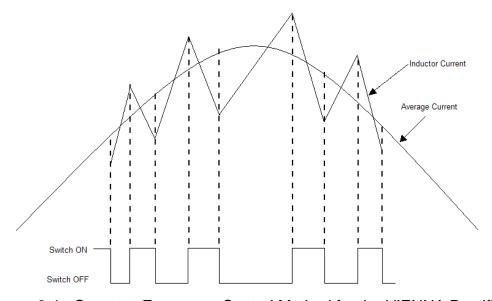

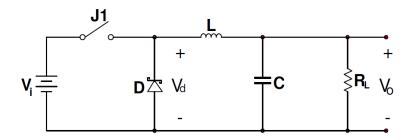

**Buck Converter** — After researching different DC-DC converters, it was found that a basic voltage divider or a linear regulator would be extremely inefficient due to the power losses associated with it. Additionally, there are ripple currents and high ripple voltage,  $\Delta$ Vo, associated with these circuits. This phenomenon is greatly reduced by using dc-dc step-down converters (buck converter) with topologies that include high switching frequency. Research showed that the two most appropriate buck converter topologies for the design were: Asynchronous buck converter and Synchronous buck converter. The main difference between these two topologies is the difference in its design.

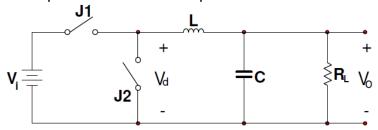

First topology is shown in Figure 2.5. This topology uses a buck convertor with a switch, diode, inductor and a capacitor. The diode in such a design is called a "free-wheeling" diode. This is because the diode eliminates or reduces any sort of fly-back voltage or voltage spikes in the inductive load as a result of sudden voltage drop in the supply voltage or if the supply voltage were to be completely removed.

Figure 2.5 - Asynchronous Buck Converter

The second topology is shown in Figure 2.6. This topology uses a buck converter with a switch and the inner diode is replaced by another switch. Ideally, this switch would be a semiconductor transistor of type BJT or MOSFET. Generally, MOSFETs are considered to be a better option. This is because BJTs require an input current to turn on and causes offset. BJTs are more desirable for designs requiring fast switching as they lack gate capacitance; although, this is at an expense of lower efficiency. MOSFETs offer better switching frequency, higher efficiency and less complexity. Comparing between PMOS and NMOS, PMOS served as a better option as it is less complex in nature.

Figure 2.6 - Synchronous Buck Converter

Looking at the two topologies, it was critical to determine the most viable design. Table 2.2 provides a detailed comparison between the two:

| Comparison           | Asynchronous                | Synchronous              |  |

|----------------------|-----------------------------|--------------------------|--|

| 1 Componente         | Uses a switch J1 (MOSFET)   | Uses two switches J1 and |  |

| 1. Components        | and diode D (Schottky Key)  | J2 (MOSFETs)             |  |

| 2. Voltage Drop      | Low forward voltage drop at | Much lower voltage drop  |  |

| 2. Voltage Drop      | the diode                   | at the MOSFET            |  |

| 3. Power Dissipation | High                        | Low                      |  |

| 4. Switching Losses  | Low                         | Negligible               |  |

| 5. Switching Speed   | Slow                        | Fast                     |  |

| 6. Efficiency        | High                        | Higher                   |  |

| 7. Total Cost        | Less expensive              | More expensive           |  |

Table 2.2 - Comparison of Synchronous versus Asynchronous Converters

A mathematical comparison between the two could be made to further clarify the most appropriate topology for the design. Other than cost and complexity of the design, the most important factors that contribute mathematically to determine efficiency would include:

- 1. Duty Cycle (D) should be lower and

- 2. Output Voltage (V<sub>o</sub>) must be higher to eliminate power dissipation losses

Realistic values were used in order to achieve goal-specific results. Accordingly, the parameter values for the design are as follows:

$$V_i = 70V, V_o = 12V, I_o = 2A$$

Utilizing basic equations for Duty Cycle and Power Loss, we can generate the values for the two topologies. At the given parameters, the voltage drop ( $V_d$ ) for a Schottky diode is known to be around 0.4V while that for a MOSFET is 0.1V (for low-voltage devices). Table 2.3 shows a comparison of power losses for synchronous and asynchronous buck converters with equal duty cycles.

| Topology        | % Duty Cycle (D)<br>V <sub>o</sub> /V <sub>i</sub> x 100 | Power Loss<br>V <sub>d</sub> I <sub>o</sub> (1-D) | % Power Loss<br>V <sub>d</sub> (1-D)/V <sub>o</sub> |

|-----------------|----------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|

| 1. Asynchronous | 17.14%                                                   | 0.66 W                                            | 2.76%                                               |

| 2. Synchronous  | 17.14%                                                   | 0.25W                                             | 0.69%                                               |

Table 2.3 - Comparison of Power Losses for Synchronous and Asynchronous Buck Converters

Similarly, the efficiency could also be compared as ~90% for asynchronous topology and ~94% for synchronous topology 1.

Looking at the comparison, the synchronous buck converter topology was chosen, neglecting its component cost which will be covered by the sponsor.

While the buck converter is a DC-DC step-down converter, combining a buck converter with a DC-DC step-up boost converter results in a buck-boost converter. This circuit can be used as either a step-up converter or a step-down converter, depending upon the duty cycle of the switching transistor.

# 2.2.3 Analog to Digital Signal Conversion

In order to transfer the power signal from the wave generator to the sensor package, it may be necessary to convert the signal from analog to digital. For this reason, conversion from analog to digital signal is researched. Analog to digital converters, or ADCs, typically consider the analog voltage or current input and convert the magnitude to a digital number. The output is generally a two's compliment binary number. These devices can vary significantly depending on the resolution, or the number of digital values that can be generated for an

analog input. Accuracy errors in ADCs are typically found in the least significant bit of the digital output, and may be the result of an aperture error. This particular error is of significant interest, as it results from clock jitter when converting time dependent analog signals to digital. Because the wave power is expected to vary with time, this error is likely to be encountered in conversion from analog to digital. The significance of the error depends on the resolution; increasing the quantity of bits in the digital output signal decreases the dependence on the least significant bit.

Analog to Digital Converters can be found in various forms. To determine the most suitable and accurate analog to Digital Converter, the first step is to determine the amount of bits required by the design. This can be determined by looking Table 2.4 which shows the resolution in ppm and dB for converter systems from 8 bits to 24 bits:

| # of Bits | 2 <sup>n</sup> | LSB<br>(FS = 1V) | Resolution (%)        | Resolution (ppm) | Resolution (dB) |

|-----------|----------------|------------------|-----------------------|------------------|-----------------|

| 8         | 256            | 3.91 mV          | 0.391                 | 3910             | 48.16           |

| 10        | 1024           | 977 μV           | 0.0977                | 977              | 60.21           |

| 12        | 4096           | 244 µV           | 0.0244                | 244              | 72.25           |

| 14        | 16384          | 61 µV            | 0.0061                | 61               | 84.29           |

| 16        | 65536          | 15.3 µV          | 0.00153               | 15.3             | 96.33           |

| 18        | 262144         | 3.81 µV          | 0.000381              | 3.81             | 108.37          |

| 20        | 1048576        | 954 nV           | 9.54x10 <sup>-5</sup> | 0.954            | 120.41          |

| 22        | 4194304        | 238 nV           | 2.38x10 <sup>-5</sup> | 0.238            | 132.45          |

| 24        | 16777216       | 59.5 nV          | 5.95x10 <sup>-6</sup> | 0.0595           | 144.46          |

Table 2.4 - Resolution amount for 8-Bit system to 24-Bit system

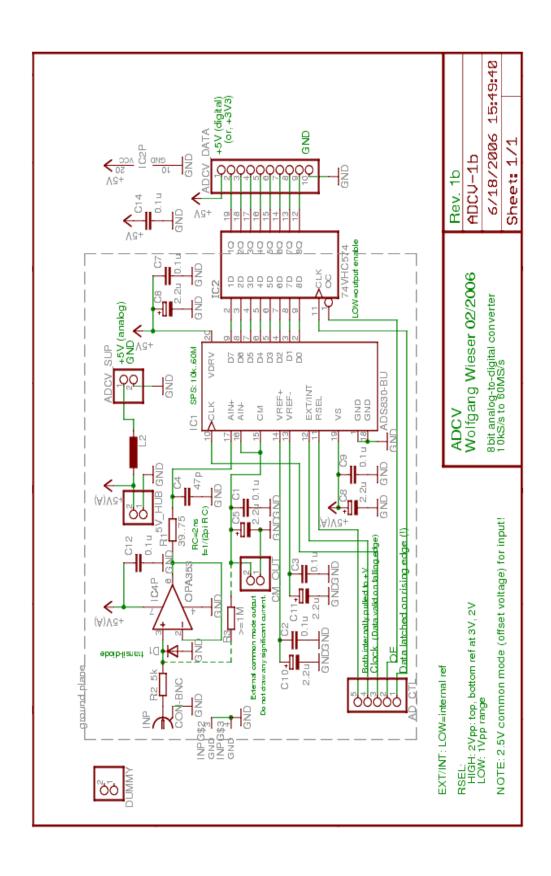

As seen in Table 2.4, high precision can be obtained by choosing the right number of bits. If the system requires a 21 bit converter, it is recommended to use 22 or 24 bit converter. This is just a precautionary measure as it allows the user to design a system that needs more bits, if necessary. An example of a circuit design for an ADC is depicted in Figure 2.4. This particular circuit design produces an 8-bit binary output from an analog input signal. The analog input is fed to a buffer amplifier at the CON-BNC connector, and the digital output leaves via the ADCV\_DATA connector.

Figure 2.7 - 8-bit Analog to Digital Converter Circuit

#### 2.2.4 MOSFET Driver

Among the possible devices that could serve as a switch for the buck converter with an LC filter, a metal oxide semiconductor field effect transistor (MOSFET) seemed ideal because of its capacity for high frequency switching, a capability that would improve the buck converter's ability to maintain a consistent output voltage. Several MOSFET drivers were investigated in order to find the best fit for this project, and they are discussed in this section.

The LM5101A 3A High Voltage High-Side and Low-Side Gate Driver from National Semiconductor is able to operate with an input voltage up to 100V, a supply voltage between 7.5V and 14V, and provide 3A of gate drive, with a listed price of \$1.35 per unit per thousand <sup>[7]</sup>. The parameters for this device are given in Table 2.5.

| Parameters                   | Values                    |

|------------------------------|---------------------------|

| Topology                     | Synchronous Buck, Bridge  |

| Input Max Voltage            | 100 Volt                  |

| Supply Minimum               | 7.5 Volt                  |

| Supply Maximum               | 14 Volt                   |

| Peak Sink Current            | 3 Amp                     |

| Peak Source Current          | 3 Amp                     |

| Output Rise Time (tr)        | 10 ns                     |

| Output Fall Time (tf)        | 10 ns                     |

| Bottom Driver Prop Delay     | 25 ns                     |

| Top Driver Propagation Delay | 25 ns                     |

| Pulse Width Min              | 50 ns                     |

| Quiescent Current            | 0.2 ma                    |

| High Side Drive              | Yes                       |

| Low Side Drive               | Yes                       |

| Outputs                      | 2                         |

| Low Gate Enable              | No                        |

| UVLO                         | Yes                       |

| Shut down                    | No                        |

| Internal Boot Diode          | Yes                       |

| Input Control                | Dual, independent         |

| Special Features             | TTL type threshold inputs |

| Reg Type                     | MOSFET Driver             |

| Temperature Minimum          | -40° C                    |

| Temperature Maximum          | 125° C                    |

Table 2.5 - Parameters for the LM5101A Driver

The ADP3625 High Speed, Dual, 4A MOSFET Driver from Analog Devices is able to operate with a supply voltage between 4.5V and 18V, providing 4A of gate drive, with a listed price of \$0.88 per unit per thousand [8]. These devices

also included internal temperature sensors with overheating shutdown at excessive junction temperatures. The parameters for this device are given in Table 2.6.

| Parameters                      | Values                                 |

|---------------------------------|----------------------------------------|

|                                 | High Speed, Dual, 4 Amp MOSFET         |

| Product Description             | Driver, inverting A & non-inv B input  |

|                                 | pins, 4.5V <vin<18v< td=""></vin<18v<> |

| V <sub>in</sub> Range (V)       | 4.5-18                                 |

| Peak Drive Current (A)          | 4                                      |

| Prop-Delay Rising (ns)          | 14                                     |

| UVLO On/Off T-Hold V typ        | 4.2 / 3.9                              |

| Precision Enable                | Yes                                    |

| Over Temperature Protection     | Yes                                    |

| Over Temperature Warning Signal | Yes                                    |

| Package                         | 8L-MSOP_VD; 8L-SOIC-EP                 |

| Temperature Range (Deg C)       | -40 to +85                             |

| Price* (1000 pcs.)              | \$0.88                                 |

Table 2.6 - Parameters for the ADP3625 Driver

The LTC4440-5 series of drivers from Linear Technology is able to operate with an input voltage up to 60V and a supply voltage between 4V and 15V, with an output of 1.1A and a listed price of \$2.50 per unit, or \$1.75 per unit per thousand <sup>[9]</sup>. The parameters for this device are given in Table 2.7.

| Parameters                      | Values          |

|---------------------------------|-----------------|

| Maximum Operating TS            | 60 V            |

| Absolute Max TS                 | 80 V            |

| MOSFET Gate Drive               | 4 V to 15 V     |

| V <sub>cc</sub> UV <sup>+</sup> | 3.2 V           |

| V <sub>cc</sub> UV              | 3.04 V          |

| INP Voltage                     | -0.3 V to 15 V  |

| BOOST Voltage (continuous)      | -0.3 V to 85 V  |

| BOOST Voltage (100 ms)          | -0.3 V to 95 V  |

| TS Voltage (continuous)         | -5 V to 70 V    |

| TS Voltage (100 ms)             | -5 V to 80 V    |

| Peak Output Current < 1 µs (TG) | 4A              |

| Temperature Range (Deg C)       | -40° C to 85° C |

| Junction Temperature            | 125° C          |

Table 2.7 - Parameters for the LTC4440-5 Driver

#### 2.2.5 Controllers

A variety of system control options were considered to handle the control portion of the power conversion. Each of the available system controllers possessed costs and benefits that needed to be weighed in order to make the best selection for this project. The costs and benefits of several controller systems are discussed in this section.

**Field Programmable Gate Arrays** — Field programmable gate arrays, or FPGAs, are integrated circuits that can be programmed by the consumer after manufacture. The ability of an FPGA to be individually programmed is a significant potential benefit, as other controllers programmed during manufacture lack flexibility. Another advantage to the FPGA is the ability to define and simulate the exact code before programming the device. One potential disadvantage is that FPGAs often occupy more space than other controller systems.

**Microcontrollers** — A microcontroller is a miniature computer built on an integrated circuit. One advantage to a microcontroller is their very small power consumption, particularly while inactive. Microcontrollers contain their own memory that may be field programmable or defined during manufacture. They are also typically very small, which can be a significant advantage when space conservation is an issue. Microcontrollers are also readily available on the market and generally inexpensive.

**Digital Signal Processors** — Digital Signal Processors, or DSPs, are a variety of microprocessor designed primarily for digital signal processing, but they often provide other features, sometimes serving as microcontrollers. Like embedded microcontrollers, they are small and often, though not invariably, inexpensive.

PIC Microcontrollers — PIC microcontrollers derive their name from Programmable Interface Controller. Some of the many benefits of PIC microcontrollers include low cost, high availability, a large number of users that has resulted in a large quantity of documentation and application notes, programming capability, low power consumption, and the capability to enter a low-power sleep state. Some of the potential drawbacks include a limited number of instructions, ranging from 35 to 80 or more, or only a single accumulator <sup>[10]</sup>. These drawbacks do not necessarily apply strictly to all PIC microcontrollers. With a very wide range of available options, a PIC microcontroller can feasibly be obtained for nearly any application desired.

A variety of PIC microcontrollers available from Microchip were investigated in order to find the best fit for this project, and they are discussed in this section.

The PIC10F222 is an inexpensive, 8-bit static Flash-based microcontroller. It uses 33 single-word / single-cycle 12-bit wide instructions. Some of its features include low power sleep current, in-circuit debugging support, and programmable code protection. The parameters for this device are given in Table 2.8.

| Parameters                  | Values       |

|-----------------------------|--------------|

| Program Memory Type         | Flash        |

| Program Memory (KB)         | 0.75         |

| Program Memory KWords       | 0.5          |

| Self-Write                  | No           |

| CPU Speed (MIPS)            | 2            |

| RAM Bytes                   | 23           |

| Max CPU Speed (MHz)         | 8            |

| Internal Oscillator         | 4 MHz, 8 MHz |

| Timers                      | 1 x 8-bit    |

| ADC                         | 2 ch, 8-bit  |

| Temperature Range (deg C)   | -40 to 125   |

| Operating Voltage Range (V) | 2 to 5.5     |

| Input / Output Pins         | 4            |

| Pin Count                   | 6            |

| Cap Touch Channels          | 2            |

| Volume Pricing              | \$0.39       |

Table 2.8 - Parameters for the PIC10F222 Microcontroller

The PIC16F886 is an inexpensive PIC microcontroller that features on-board EEPROM data memory, an analog comparator, an internal oscillator with selectable 8 MHz – 32 KHz, and programmable on-chip voltage reference. The parameters for this device are given in Table 2.9.

| Parameters                  | Values                |  |  |

|-----------------------------|-----------------------|--|--|

| Program Memory Type         | Flash                 |  |  |

| Program Memory (KB)         | 3.5                   |  |  |

| Program Memory KWords       | 2                     |  |  |

| Self-Write                  | No                    |  |  |

| CPU Speed (MIPS)            | 5                     |  |  |

| RAM Bytes                   | 128                   |  |  |

| Data EEPROM (bytes)         | 256                   |  |  |

| Max CPU Speed (MHz)         | 20                    |  |  |

| Internal Oscillator         | 8 MHz, 32 kHz         |  |  |

| Timers                      | 2 x 8-bit, 1 x 16-bit |  |  |

| ADC                         | 4 ch, 10-bit          |  |  |

| Comparators                 | 1                     |  |  |

| Temperature Range (deg C)   | -40 to 125            |  |  |

| Operating Voltage Range (V) | 2 to 5.5              |  |  |

| Input / Output Pins         | 6                     |  |  |

| Pin Count                   | 8                     |  |  |

| Cap Touch Channels          | 3                     |  |  |

| Volume Pricing              | \$0.91                |  |  |

Table 2.9 - Parameters for the PIC12F683 Microcontroller

The PIC16F886 is an 8-bit Flash-based CMOS PIC microcontroller with features that include self-programming, two comparators, a power saving sleep mode, and in-circuit debugging. The parameters for this device are given in Table 2.10.

| Parameters                        | Values                       |

|-----------------------------------|------------------------------|

| Program Memory Type               | Flash                        |

| Program Memory (KB)               | 14                           |

| Program Memory KWords             | 8                            |

| Self-Write                        | Yes                          |

| CPU Speed (MIPS)                  | 5                            |

| RAM Bytes                         | 368                          |

| Data EEPROM (bytes)               | 256                          |

| Max CPU Speed (MHz)               | 20                           |

| Internal Oscillator               | 8 MHz, 32 kHz                |

| Digital Communication Peripherals | 1-A/E/USART, 1-MSSP(SPI/I2C) |

| Capture/Compare/PWM Peripherals   | 1 CCP, 1 ECCP                |

| Timers                            | 2 x 8-bit, 1 x 16-bit        |

| ADC                               | 4 ch, 10-bit                 |

| Comparators                       | 2                            |

| Temperature Range (deg C)         | -40 to 125                   |

| Operating Voltage Range (V)       | 2 to 5.5                     |

| Input / Output Pins               | 6                            |

| Pin Count                         | 28                           |

| Cap Touch Channels                | 11                           |

| Volume Pricing                    | \$1.49                       |

Table 2.10 - Parameters for the PIC16F886 Microcontroller

The PIC18F2620 is an 8-bit Flash-based CMOS PIC microcontroller with features that include a failsafe clock monitor, two comparators, run, idle, and sleep modes, and C compiler optimized RISC architecture. The parameters for this device are given in Table 2.11.

| Parameters                        | Values                       |

|-----------------------------------|------------------------------|

| Program Memory Type               | Flash                        |

| Program Memory (KB)               | 64                           |

| Program Memory KWords             | 32                           |

| Self-Write                        | Yes                          |

| CPU Speed (MIPS)                  | 10                           |

| RAM Bytes                         | 3968                         |

| Data EEPROM (bytes)               | 1024                         |

| Max CPU Speed (MHz)               | 40                           |

| Internal Oscillator               | 8 MHz, 32 kHz                |

| Digital Communication Peripherals | 1-A/E/USART, 1-MSSP(SPI/I2C) |

| Capture/Compare/PWM Peripherals   | 2 CCP                        |

| Timers                            | 1 x 8-bit, 3 x 16-bit        |

| ADC                         | 10 ch, 10-bit |

|-----------------------------|---------------|

| Comparators                 | 2             |

| Temperature Range (deg C)   | -40 to 125    |

| Operating Voltage Range (V) | 2 to 5.5      |

| Input / Output Pins         | 25            |

| Pin Count                   | 28            |

| Volume Pricing              | \$4.06        |

Table 2.11 - Parameters for the PIC18F2620 Microcontroller

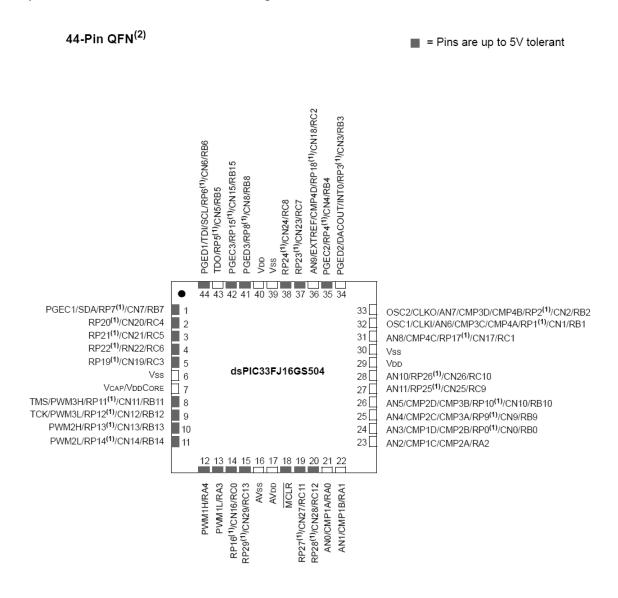

The dsPIC33FJ16GS504 is a 16-bit digital signal controller with features that include a failsafe clock monitor, two high speed analog comparators, run, idle, and sleep modes, and C compiler optimized instruction set. The parameters for this device are given in Table 2.12.

| Parameters                        | Values                       |

|-----------------------------------|------------------------------|

| Program Memory Type               | Flash                        |

| Program Memory (KB)               | 16                           |

| Program Memory KWords             | 32                           |

| Self-Write                        | Yes                          |

| CPU Speed (MIPS)                  | 40                           |

| RAM Bytes                         | 2048                         |

| Data EEPROM (bytes)               | 0                            |

| Max CPU Speed (MHz)               | 40                           |

| Internal Oscillator               | 7.37 MHz, 32 kHz             |

| nanoWatt Features                 | Fast Wake/Fast Control       |

| Digital Communication Peripherals | 1-UART, 1-SPI, 1-I2C         |

| Analog Paripharala                | 2-A/D 12x10-bit @ 4000(ksps) |

| Analog Peripherals                | 4-D/A 1x10-bit @ 640(ksps)   |

| Timers                            | 2 x 16-bit                   |

| 16-bit PWM resolutions            | 16                           |

| Motor Control PWM Channels        | 8                            |

| Comparators                       | 4                            |

| Temperature Range (deg C)         | -40 to 125                   |

| Operating Voltage Range (V)       | 3 to 3.6                     |

| Input / Output Pins               | 35                           |

| Pin Count                         | 44                           |

| Volume Pricing                    | \$3.42                       |

Table 2.12 - Parameters for the dsPIC33FJ16GS504 Microcontroller

The PIC microcontroller was determined to be the most appropriate choice for this project. PIC microcontrollers are readily available with a wide array of available parameters making them a good fit for many applications. They are inexpensive and highly versatile. For the purposes of this project, the 16-bit dsPIC33FJ16GS504 microcontroller was determined to be the optimal choice for its low cost, programmability with the C programming language, four

comparators, power saving features, and high maximum CPU speed. The pin layout for this device is shown in Figure 2.8.

- Note 1: The RPn pins can be used by any remappable peripheral. See the "dsPlC33FJ06GS101/X02 and dsPlC33FJ16GSX02/X04 Controller Families" table for the list of available peripherals.

- 2: The metal plane at the bottom of the device is not connected to any pins and is recommended to connect to Vss externally

Figure 2.8 - Pin Layout for the dsPIC33FJ16GS504 PIC Microcontroller (Permission requested from Microchip)

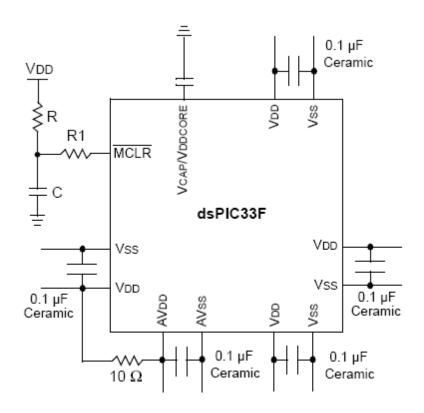

Descriptions for the pin inputs and outputs for the dsPIC33FJ16GS504 PIC are given in Figure 2.9 and Figure 2.10.

| Pin Name      | Pin<br>Type | Buffer<br>Type | PPS<br>Capable | Description                                                                  |

|---------------|-------------|----------------|----------------|------------------------------------------------------------------------------|

| CMP1A         | Т           | Analog         | No             | Comparator 1 Channel A                                                       |

| CMP1B         | - 1         | Analog         | No             | Comparator 1 Channel B                                                       |

| CMP1C         | - 1         | Analog         | No             | Comparator 1 Channel C                                                       |

| CMP1D         | - 1         | Analog         | No             | Comparator 1 Channel D                                                       |

| CMP2A         | - 1         | Analog         | No             | Comparator 2 Channel A                                                       |

| CMP2B         | - 1         | Analog         | No             | Comparator 2 Channel B                                                       |

| CMP2C         | - 1         | Analog         | No             | Comparator 2 Channel C                                                       |

| CMP2D         | - 1         | Analog         | No             | Comparator 2 Channel D                                                       |

| CMP3A         | - 1         | Analog         | No             | Comparator 3 Channel A                                                       |

| CMP3B         | - 1         | Analog         | No             | Comparator 3 Channel B                                                       |

| CMP3C         | - 1         | Analog         | No             | Comparator 3 Channel C                                                       |

| CMP3D         | - 1         | Analog         | No             | Comparator 3 Channel D                                                       |

| CMP4A         | - 1         | Analog         | No             | Comparator 4 Channel A                                                       |

| CMP4B         | - 1         | Analog         | No             | Comparator 4 Channel B                                                       |

| CMP4C         | - 1         | Analog         | No             | Comparator 4 Channel C                                                       |

| CMP4D         | ı           | Analog         | No             | Comparator 4 Channel D                                                       |

| DACOUT        | 0           | _              | No             | DAC output voltage                                                           |

| ACMP1-ACMP4   | 0           | _              | Yes            | DAC trigger to PWM module                                                    |

| EXTREF        | ı           | Analog         | No             | External voltage reference input for the reference DACs                      |

| REFCLKO       | 0           | _              | Yes            | REFCLKO output signal is a postscaled derivative of the system clock         |

| FLT1-FLT8     | - 1         | ST             | Yes            | Fault Inputs to PWM module                                                   |

| SYNCI1-SYNCI2 | - 1         | ST             | Yes            | External synchronization signal to PWM Master Time Base                      |

| SYNCO1        | 0           | _              | Yes            | PWM master time base for external device synchronization                     |

| PWM1L         | 0           | _              | No             | PWM1 low output                                                              |

| PWM1H         | 0           | _              | No             | PWM1 high output                                                             |

| PWM2L         | 0           | _              | No             | PWM2 low output                                                              |

| PWM2H         | 0           | _              | No             | PWM2 high output                                                             |

| PWM3L         | 0           | _              | No             | PWM3 low output                                                              |

| PWM3H         | 0           | _              | No             | PWM3 high output                                                             |

| PWM4L         | 0           | _              | Yes            | PWM4 low output                                                              |

| PWM4H         | 0           | _              | Yes            | PWM4 high output                                                             |

| PGED1         | I/O         | ST             | No             | Data I/O pin for programming/debugging communication Channel 1               |

| PGEC1         | 1           | ST             | No             | Clock input pin for programming/debugging communication<br>Channel 1         |

| PGED2         | I/O         | ST             | No             | Data I/O pin for programming/debugging communication Channel 2               |

| PGEC2         | ı           | ST             | No             | Clock input pin for programming/debugging communication<br>Channel 2         |

| PGED3         | I/O         | ST             | No             | Data I/O pin for programming/debugging communication Channel 3               |

| PGEC3         | ı           | ST             | No             | Clock input pin for programming/debugging communication<br>Channel 3         |

| MCLR          | I/P         | ST             | No             | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |

| AVDD          | Р           | Р              | No             | Positive supply for analog modules. This pin must be connected at all times. |

| AVss          | Р           | Р              | No             | Ground reference for analog modules                                          |

| VDD           | Р           | _              | No             | Positive supply for peripheral logic and I/O pins                            |

| VCAP/VDDCORE  | Р           | _              | No             | CPU logic filter capacitor connection                                        |

| Vss           | Р           | _              | No             | Ground reference for logic and I/O pins                                      |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

$\begin{array}{ll} \mbox{Analog = Analog input} & \mbox{I = Input} \\ \mbox{P = Power} & \mbox{O = Output} \end{array}$

TTL = Transistor-Transistor Logic PPS = Peripheral Pin Select

Figure 2.9 - Pin Description for the dsPIC33FJ16GS504 PIC Microcontroller (Permission requested from Microchip)

| Pin Name     | Pin<br>Type | Buffer<br>Type | PPS<br>Capable | Description                                                                                                                                                                        |

|--------------|-------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN11     | ı           | Analog         | No             | Analog input channels                                                                                                                                                              |

| CLKI         | 1           | ST/CMOS        | No             | External clock source input. Always associated with OSC1 pin function.                                                                                                             |

| CLKO         | 0           | _              | No             | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1         | 1           | ST/CMOS        | No             | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |

| osc2         | I/O         | _              | No             | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| CN0-CN29     | I           | ST             | No             | Change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                   |

| IC1-IC2      | 1           | ST             | Yes            | Capture inputs 1/2                                                                                                                                                                 |

| OCFA         | ı           | ST             | Yes            | Compare Fault A input (for Compare Channels 1 and 2)                                                                                                                               |

| OC1-OC2      | 0           | _              | Yes            | Compare Outputs 1 through 2                                                                                                                                                        |

| INT0         | 1           | ST             | No             | External Interrupt 0                                                                                                                                                               |

| INT1         | !           | ST             | Yes            | External Interrupt 1                                                                                                                                                               |

| INT2         | 1           | ST             | Yes            | External Interrupt 2                                                                                                                                                               |

| RA0-RA4      | I/O         | ST             | No             | PORTA is a bidirectional I/O port                                                                                                                                                  |

| RB0-RB15     | I/O         | ST             | No             | PORTB is a bidirectional I/O port                                                                                                                                                  |

| RC0-RC13     | I/O         | ST             | No             | PORTC is a bidirectional I/O port                                                                                                                                                  |

| RP0-RP29     | I/O         | ST             | No             | Remappable I/O pins                                                                                                                                                                |

| T1CK         | - 1         | ST             | Yes            | Timer1 external clock input                                                                                                                                                        |

| T2CK         |             | ST             | Yes            | Timer2 external clock input                                                                                                                                                        |

| T3CK         | 1           | ST             | Yes            | Timer3 external clock input                                                                                                                                                        |

| U1CTS        | 1           | ST             | Yes            | UART1 clear to send                                                                                                                                                                |

| U1RTS        | 0           | _              | Yes            | UART1 ready to send                                                                                                                                                                |

| U1RX<br>U1TX | 0           | ST             | Yes<br>Yes     | UART1 receive<br>UART1 transmit                                                                                                                                                    |

| SCK1         | 1/0         | ST             | Yes            | Synchronous serial clock input/output for SPI1                                                                                                                                     |

| SDI1         | "/          | ST             | Yes            | SPI1 data in                                                                                                                                                                       |

| SDO1         | l ò         | _              | Yes            | SPI1 data out                                                                                                                                                                      |

| SS1          | I/O         | ST             | Yes            | SPI1 slave synchronization or frame pulse I/O                                                                                                                                      |

| SCL1         | I/O         | ST             | No             | Synchronous serial clock input/output for I2C1                                                                                                                                     |

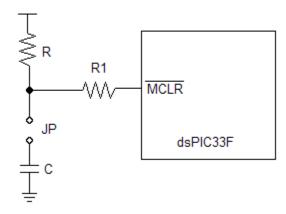

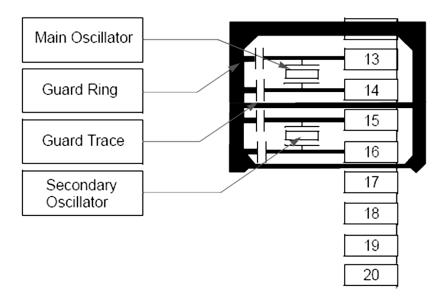

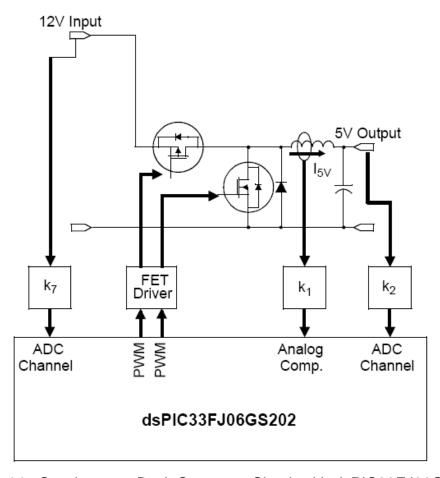

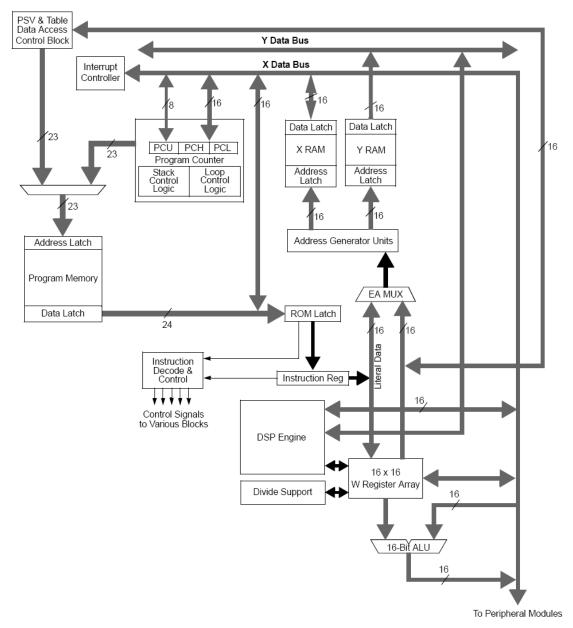

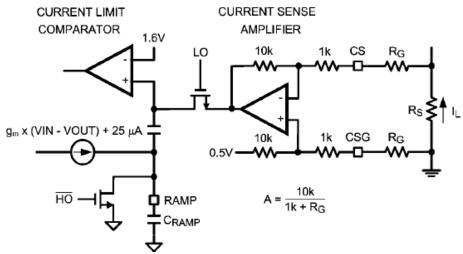

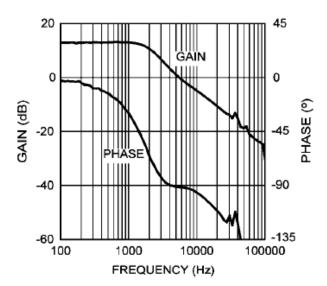

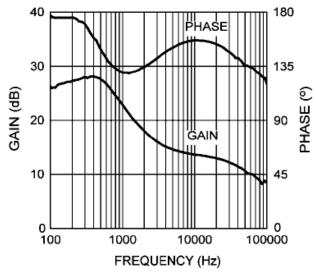

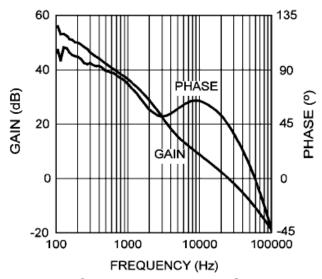

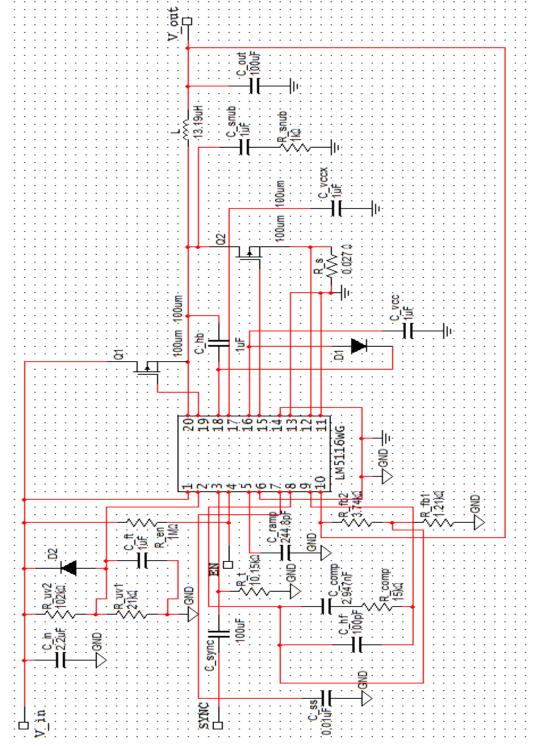

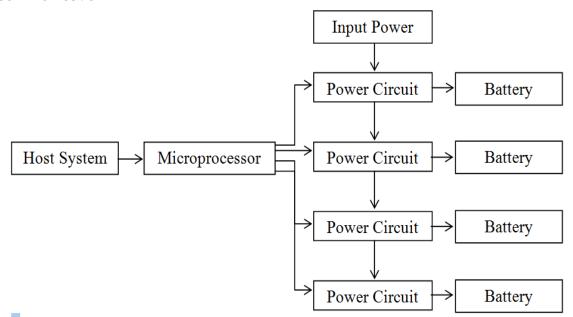

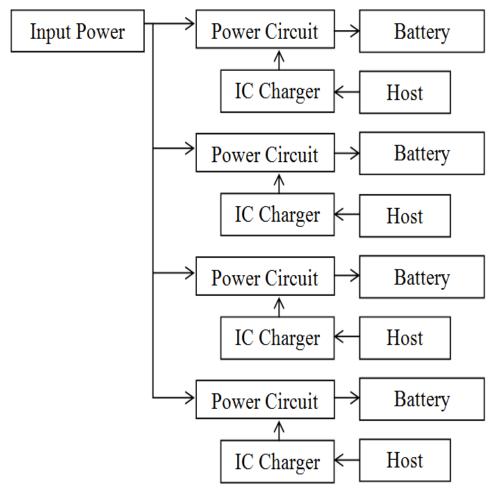

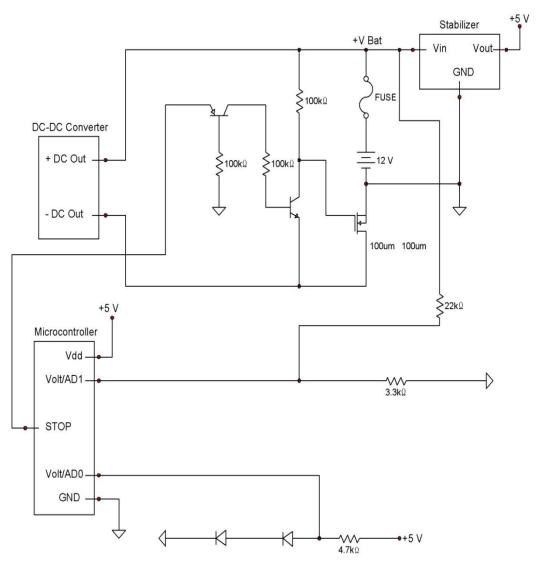

| SDA1         | I/O         | ST             | No             | Synchronous serial data input/output for I2C1                                                                                                                                      |